Verilog基础之十一、移位寄存器实现

(资料图)

(资料图)

一、前言

移位寄存器SRL在工程中属于使用频率较高个模块,可用于存储数据,实现串并转换;根据数据移动方向可分为左移寄存器,右移寄存器,左移是向数据高位移动,右移是向数据低位移动。

二、工程设计

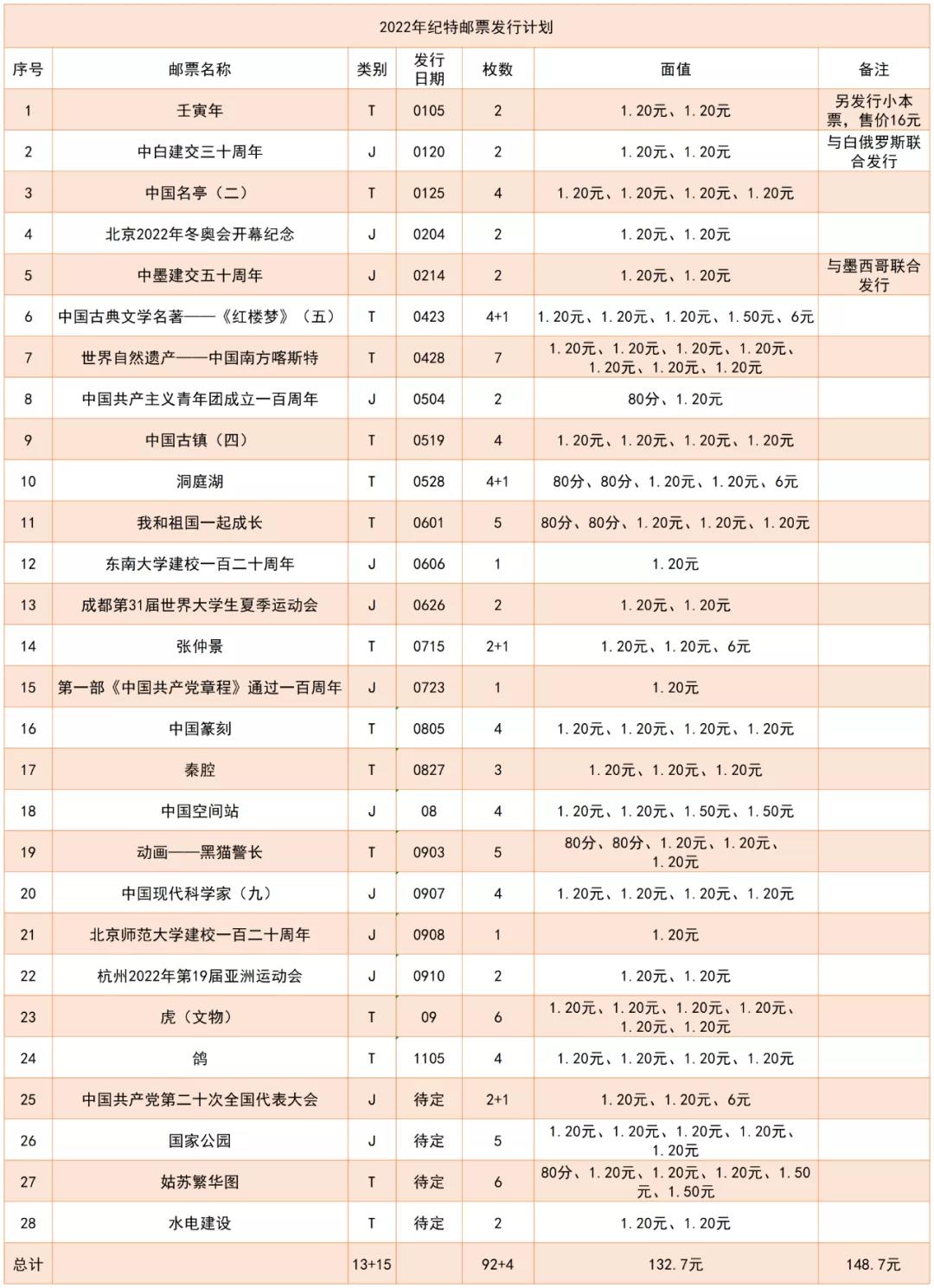

工程代码

工程中包含了左移,右移,循环移位的设计,输出为8位。左移即输入不断从右边进入,同理,右移为输入不断从左边加入,循环移位此处为右循环,每一次变化都是第一位移到最高位,其他位都右移一位。

测试代码如下,使用系统random生成随机数作为输入

综合结果

根据综合结果,左移和右移实现上为位置的对调,循环移位因为无需输入,故综合后只有输出

仿真结果

在红框1所在的时刻,输入in为0,out_l为10011111,out_r为11111001,out_c为10001100。在时钟clk的上升沿到来时,进行移位,左移out_l右边加0变为00111110,右移out_r左边加0变为01111100,out_c循环移位变为01000110。

红框2所在的时刻,输入in为1,在第二个时钟clk的上升沿到来时out_l变为01111101,out_r变为10111110,out_c循环移位变为00100011。符合预期

关键词:

推荐阅读

世界黄金协会更新了2022年的黄金产量数据,据金属聚焦公司的最新估算,

2023-06-26 18:47:36

智通财经APP讯,汇宇制药(688553 SH)发布公告,公司确定2023年限制性股

2023-06-26 16:54:04

摘要:2023年06月26日银之杰(300085)股价大幅跳水6 91%,该股报11 71

2023-06-26 14:26:50

财经网医药讯腾盛博药6月26日宣布,公司与QpexBiopharma(Qpex)达成最

2023-06-26 11:59:48

资讯

品牌